I’ve lost track of this discussion, but I very much would like to get a prototype made.

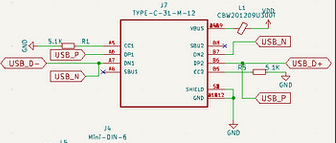

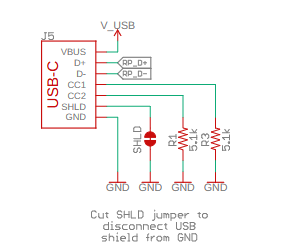

USB C

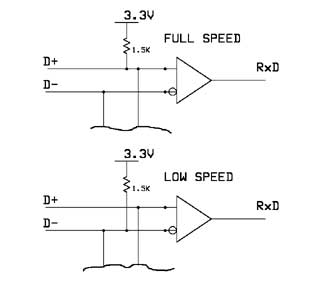

We do this cross connect of USB_P and USB_N, which I understand was needed to tell the USB host that we are USB 1.0 or 2.0 device.

SparkFun does it differently, but their connector is only 6 pins so maybe the connections are made internally.

- I’m not sure if it is something to be concerned about.

PS/2 sniffing

Sniffing is tested. In sniffing mode the Bus Pirate is a passive listener and the IO buffers are input. The bus is 5volts and the power is 5volts.

PS/2 Host

@Dreg have you managed to test this on the Bus Pirate through the IO buffers? It will be different than using a bare pico.

PS/2 is a bidirectional, open drain protocol where the clock is always provided by the device.

The program should be structured like I2C.pio: Enable GPIO pin pull-down (on 5, 6 has the big pull-down to fix E9), then manipulate the IO buffer direction pin between input and output to release or hold low the bus.

Input should be read from the GPIO when the buffer is input, or use one pin for high/low, and a second pin for input. I kind of think this would take two PIO programs, Tx and Rx with an interrupt or GPIO to stall TX when RX.

USB sniffing

Also tested. IO buffers passive input. Bus is 3.3volts (IO pins/vout at 3.3volts), device is powered by host VUSB (4.75-5.25v) with VOUT selection switch off.

- This seems fine

- Could add a a TVS diode for protection of D+/D- as mentioned by @electronic_eel

USB keyboard host

Device needs 4.75 to 5.25 volts, but the IO is 3.3volts. The buffers are CMOS so the minimum high when VOUT is 5volts is 3.5-3.7v. The Bus Pirate can’t power the device and view the high level of USB at the same time.

This is perhaps a Bus Pirate short coming. Maybe there should be a way to choose what voltage to run the IO buffers independent of the VOUT. Even two options:

- Powered by VOUT

- Powered by 3.3volt internal supply

So the current proposal is to add:

- 3.3volt regulator

- 2 additional bidirectional buffers

This adds two layer of buffers to switch, signal delay, switch noise/delays, etc. it also makes the PIO program much more complicated. You’ll probably want to use side set to control the buffer IO direction, but those pins are limited (5?) and must be consecutive.

As with PS/2 host, it might be a bit easier to use sepeerate pins for high/low and input (could be the FALA buffer on 6+).

It probably needs to straddle the boundary between the buffer direction pins and the buffer IO pins. IO6/7 would be data/clock and IO 0(/1?) would be direction. This will take some big planning, and the pin arrangements may not allow all these modes to share the same plank at all. I suggest you make something up on a perfboard or breadboard to get a feel.

-

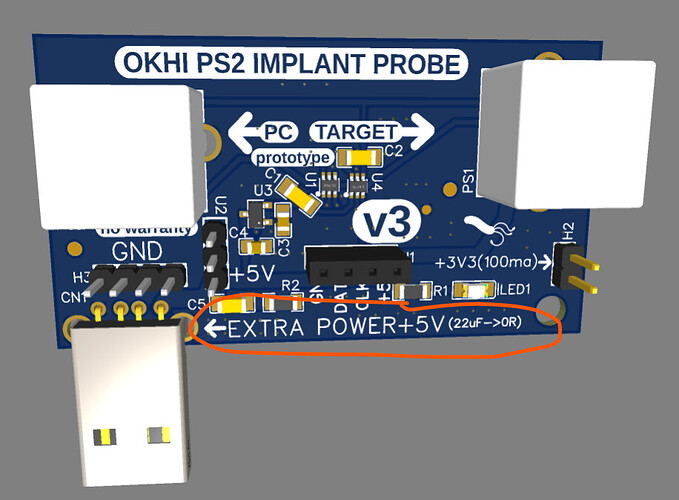

An easy alternative is to add a 5volt regulator and use an external supply. The supply could be via the unused USB A or C connector with a “power only cable” or power bank/USB charger. We could even add a second “power only” USB C connector with no data lines connected.

-

Alternately a small SMPS to boost 3.3v to 5volts. However it now has a clock so the board will need full FCC/CE compliance testing.

I would focus on solving the USB 5 volt supply issue (easy) compared to some double buffer madness via the PIO. I realize it doesn’t satisfy the “completeness” urge.

Other USB host & device (?)

- Same power issues

- Same double buffer

I really doubt with the Bus Pirate IO buffers (double for two layers) you will be able to do much more than a Full Speed host (if that).

There is is also some speed indication from host (bus pirate) to device (?) using a pull-down resistor on the USB C connector pins(?). I have a whole lot of gaps in my knowledge here. For this we add a four way switch with values for:

- Sniffing (no resistors)

- Host mode (pulldowns to be able to detect the device’s pullups)

- Lowspeed Device (<=12MBPS)

- Highspeed Device (480MBPS)*

* I realize now you may mean low speed vs full speed? I am folding the info below because I’m almost certain you mean full speed after reading the thread again. Don’t LS and FS have the same pull-down value (5.1K)?

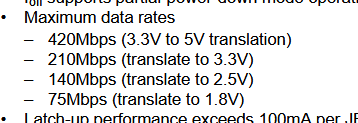

Why High speed USB probably isn't possible

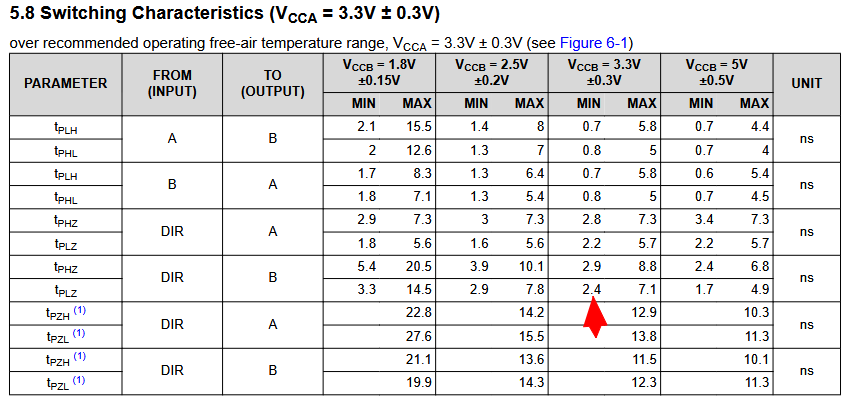

The max speed even for 3.3 to 5v is less than USB High speed. We’ll be doing 3.3v to 3.3v which is about half that. Also, is the PIO really capable of operating at 480mhz or above? I guess the device may have a fall back?

Don’t forget to factor in direction switching time (perhaps x2, depending on how it is controlled).

Things I can’t match to a feature

Suggestion to add 3.3volt VREG and 1t45 buffers fixed to input to avoid pushing 5.0v accidentally into a device. I assume this is for a sniffer only board? Otherwise they have to be manipulated for the USB keyboard host.

Closing thoughts

I’d like to hear if @dreg has successfully done a PS/2 host (and then USB host) via the Bus Pirate buffered IOs.

If not, that will be a project unto itself. I suspect it will reveal the amount of sorcery needed to make this all work through double buffers, let alone in a single unified plank.