Firmware

bus_pirate-el-dr-gusman-la.zip (126.4 KB)

This is a test firmware for El Dr. Gusman Logic Analyzer . The logic analyzer blocks all the other Bus Pirate functions in this test, it will be integrated soon.

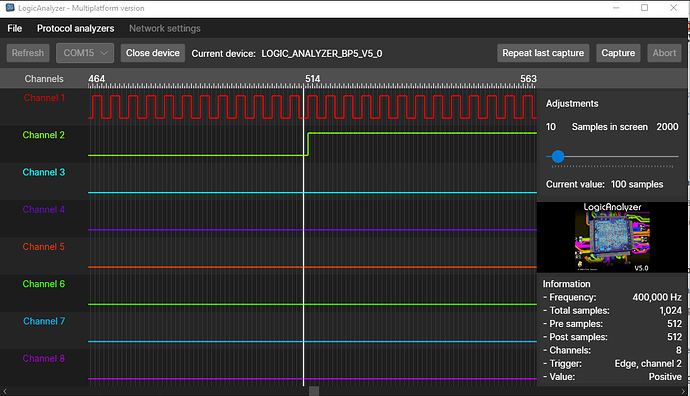

This is a sample and dump logic analyzer with hardware triggers in the PIO. It waits for the trigger and then records as many pre/post trigger samples specified, up to the buffer maximum (138K). Speeds up to 100MSPS are possible.

Custom client

El Dr. Gusman’s Logic Analyzer project uses a custom UI available for all (most?) platforms.

This type of logic analyzer is easy to port to the SUMP protocol, then it will work with sigrok out of the box, as well as a number of other software UIs.

UARTs/configuration

Two UARTs will connect in this firmware. The lower number does nothing, the higher number is used by the logic analyzer.

Remember to power the buffer

Put some kind of voltage on the VOUT/VREF pin to power the Bus Pirate IO buffer or the logic analyzer won’t record anything. This allows compatibility with a wide range of logic levels in the 1.8-5.0volt range. In the future it would be nice to use the Bus Pirate power supply and allow the voltage to be set from the client.

Danger! Overclocked!

The firmware overclocks the RP2040 to 200MHz. Evidently most (all?) boards will work at this speed. If you have a problem please let me know.

Only simple edge triggers

Using the complex triggers uses up two IO pins that have to be tied together. For now it supports simple triggers only.