clock_gettime(CLOCK_MONOTONIC, {tv_sec=26566, tv_nsec=712387927}) = 0

timerfd_settime(4, TFD_TIMER_ABSTIME, {it_interval={tv_sec=0, tv_nsec=0}, it_value={tv_sec=26567, tv_nsec=712387927}}, NULL) = 0

ioctl(7, USBDEVFS_SUBMITURB, 0x55fb9f67ded0) = 0

poll([{fd=3, events=POLLIN}, {fd=4, events=POLLIN}, {fd=7, events=POLLOUT}], 3, 60000) = 1 ([{fd=7, revents=POLLOUT}])

ioctl(7, USBDEVFS_REAPURBNDELAY, 0x7ffe3fd145f0) = 0

timerfd_settime(4, 0, {it_interval={tv_sec=0, tv_nsec=0}, it_value={tv_sec=0, tv_nsec=0}}, NULL) = 0

ioctl(7, USBDEVFS_REAPURBNDELAY, 0x7ffe3fd145f0) = -1 EAGAIN (Resource temporarily unavailable)

write(2, "warning: ", 9warning: ) = 9

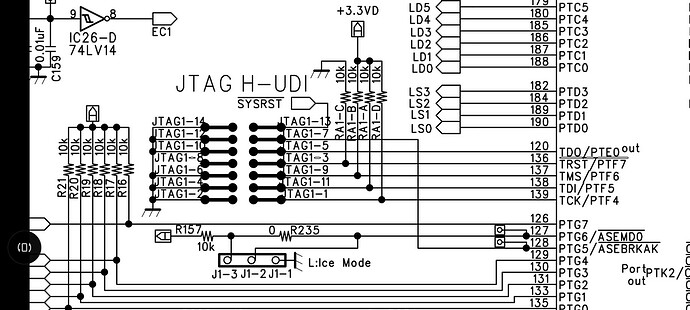

write(2, "TDO seems to be stuck at 1\n", 27TDO seems to be stuck at 1

) = 27

This is what I get when I run detect on urjtag with strace. I am particulary worried about:

ioctl(7, USBDEVFS_REAPURBNDELAY, 0x7ffe3fd145f0) = -1 EAGAIN (Resource temporarily unavailable)

But not sure now if it’s not trying to open other USB devices

Edit:

I think I will swap TDI and TDO maybe thats the issue here. But not today. Swapped there and back same results. Or once detect finished but no chip detected.