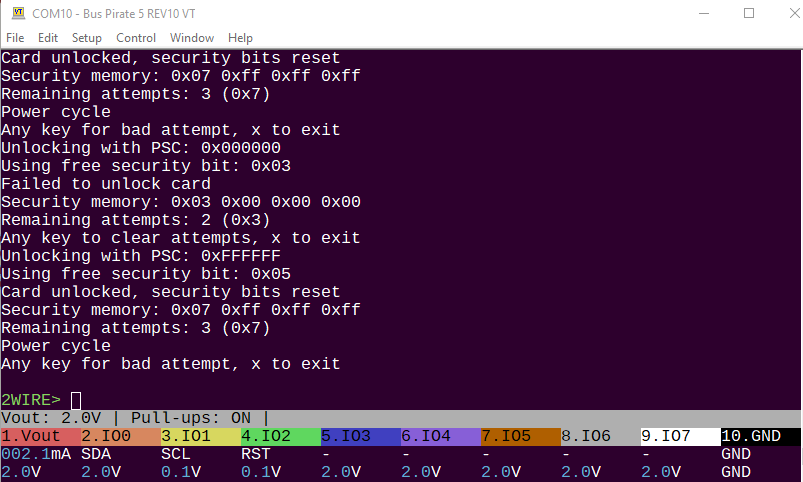

Wrote a loop to power cycle, pause, enter wrong password, pause, enter correct password and reset counter.

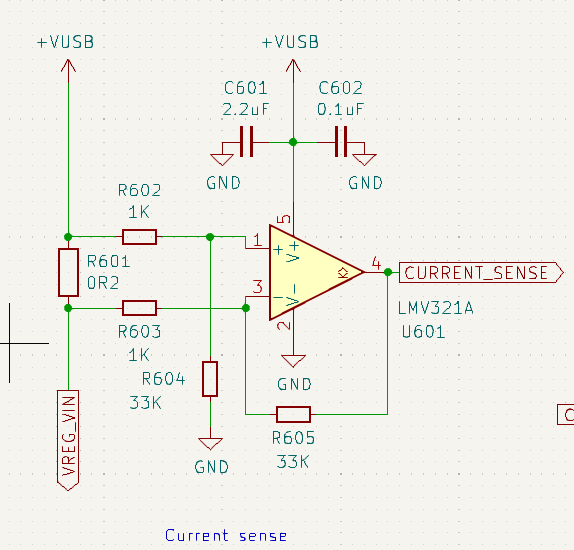

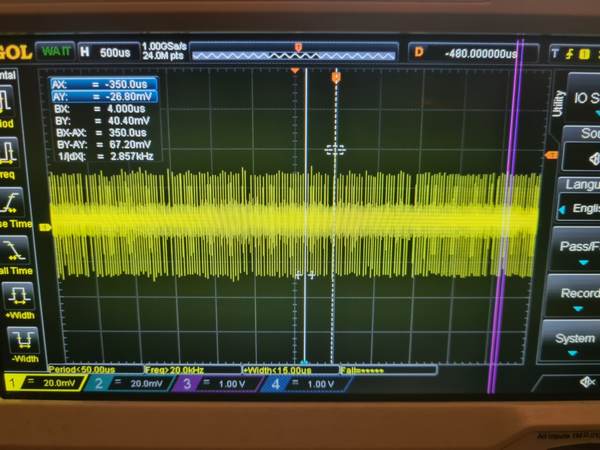

Measured the output of the current sense op-amp from pin 4 with my scope.

Alas, no repeatable triggering above the noise floor. This is probably because we’re measuring before about 10uF of capacitors, which are absorbing the big hit.

All is not lost. We can make an external version of the sense circuit and put between the card and all caps. The Bus Pirate iSense scales 0-500mA to a 0-3.3volt output, and uses a 0.2 ohm resistor.

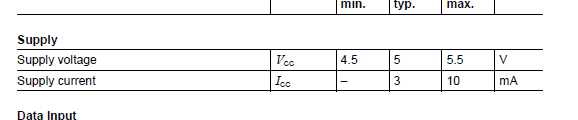

Conveniently they don’t specify read/write/erase current in the datasheet. But, an isense that is 10ma or 12ma max will give a lot more resolution on small changes. A bigger voltage drop resistor would get rid of some noise because the op-amp gain will be a lot less.

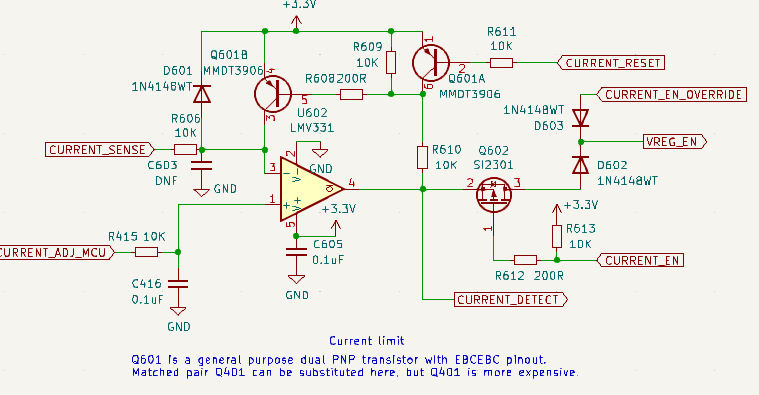

I’ve only ever seen this done with an FPGA, so maybe we can’t react fast enough with the RP2040. In that case, something like the current limit circuit controlling all IO pins and power through PFETs would be even faster than an FPGA and a lot cheaper.