Continuing from Buspirate v5 rev 10 SPI Delay - Cannot dump chip:

Today, I built / flashed latest main (0d8d8da from last week, "Update to latest version of minmea gps decoder).

I then attached the WSON8 plank (REV3), filling the 6x8 slot with a chip that I really want to get a dump of. Unfortunately, I wasn’t getting any response from the chip. I remember having this type of problem before, so I search the archives and found the above thread. So I manually set BPIO 0..3 to HLHH, following that thread’s learnings.

BusPirate terminal commands

HiZ> m spi

Mode: SPI

Use previous settings?

SPI speed: 10 kHz

Data bits: 8

Clock polarity: Idle LOW

Clock phase: LEADING edge

Chip select: Active LOW (/CS)

y/n, x to exit (Y) > y

SPI> A 1

IO1 set to OUTPUT: 1

SPI> A 0

IO0 set to OUTPUT: 1

SPI> a 1

IO1 set to OUTPUT: 0

SPI> A 2

IO2 set to OUTPUT: 1

SPI> A 3

IO3 set to OUTPUT: 1

SPI> flash probe

Initializing SPI flash...

Flash device manufacturer ID 0x00, type ID 0x00, capacity ID 0x00

Error: SFDP signature error. It must be 0x50444653 'SFDP'

Warning: Read SFDP parameter header information failed.

Warning: The chip does not support JEDEC SFDP.

Searching flash chip database for 0x00 0x00 0x00

Error: Flash device not found

Error: device not detected

SPI>

Unfortunately, still no signs of life.

Thinking I somehow killed the chip (e.g., overheating? if that’s even a thing?), I grabbed the WSON8 I saved from an alpha BP7 board, and put that into the adapter. Unfortunately, I got the same result.

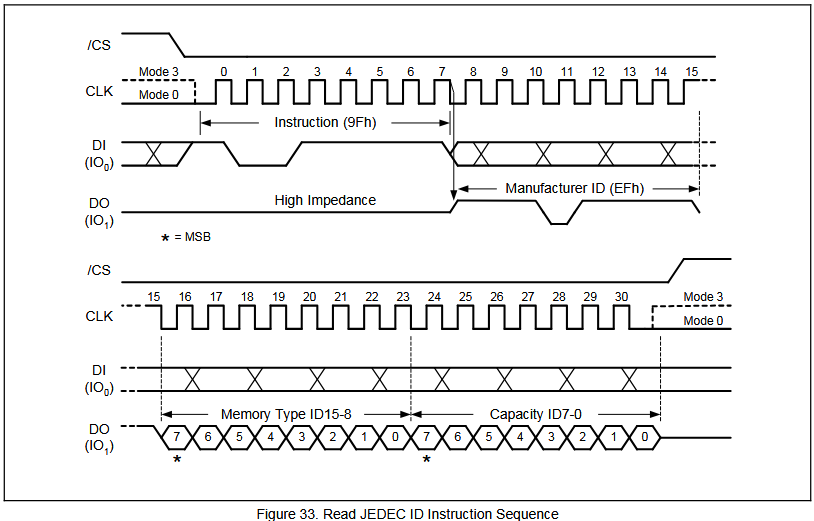

The chip is a WINBOND W25N01GVxxxG/T/R (datasheet). Nothing jumps out at me as problematic…

So I dug deeper. flash probe was reporting the following line of output:

Flash device manufacturer ID 0x00, type ID 0xEF, capacity ID 0xAA

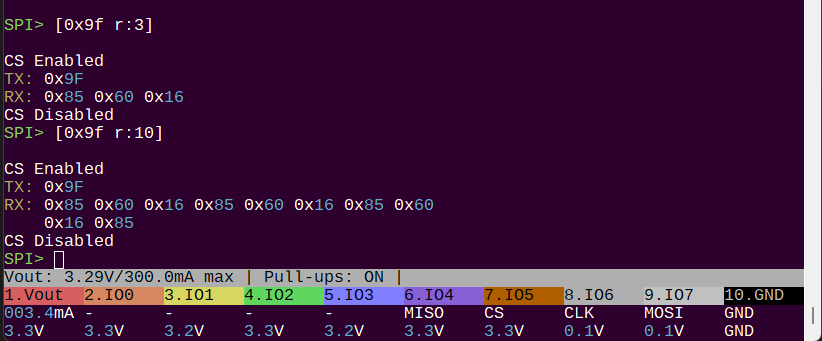

However, using bus syntax, manually requesting the JEDEC ID worked fine:

SPI> [ 0xFF ] D:100 [ 0x9F r:4 ]

...

TX: 0x9F

RX: 0x00 0xEF 0xAA 0x21

Is the flash probe command broken, where it fails to skip over the first dummy byte (here, 0x00)? Obviously, if it’s reading at the wrong byte offset, it won’t properly identify the chip.

Both the recovered BP7 and new WSON8 chips seemed to work properly using bus syntax, and failed the same way using flash probe.

I would welcome any thoughts. Also, I may be slow to respond until Monday…