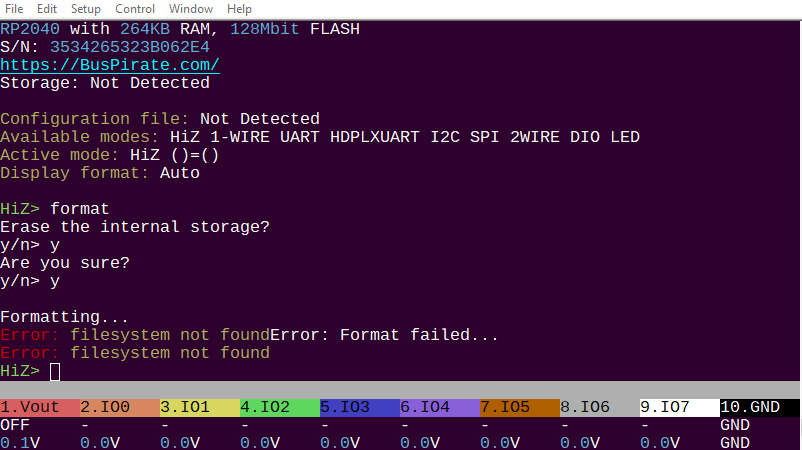

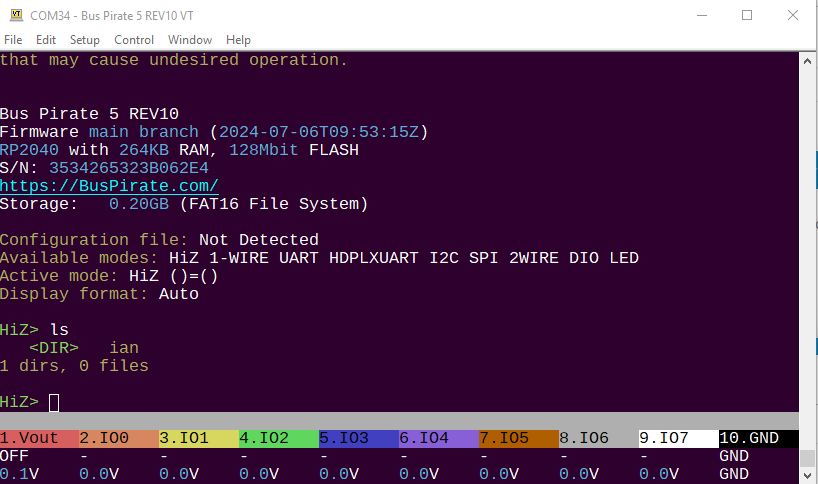

A blast of hot air got the chip properly seated. It’s returning the right codes now, but fatFS is not able to format it.

// public function definitions

DSTATUS diskio_initialize(BYTE drv)

{

if (drv) return STA_NOINIT; /* Supports only drive 0 */

// init flash management stack

int ret = spi_nand_init();

if (SPI_NAND_RET_OK != ret) {

printf("spi_nand_init failed, status: %d.", ret);

return STA_NOINIT;

}

// init flash translation layer

dhara_map_init(&map, &nand, page_buffer, 4);

dhara_error_t err = DHARA_E_NONE;

ret = dhara_map_resume(&map, &err);

printf("dhara resume return: %d, error: %d", ret, err);

// map_resume will return a bad status in the case of an empty map, however this just

// means that the file system is empty

// TODO: Flag statuses from dhara that do not indicate an empty map

initialized = true;

return 0;

}

In nand_ftl_diskio.c:

- spi_nand_init() returns success! Yeah!

- dhara_map_resume(&map, &err) returns [DHARA_E_TOO_BAD] = “Too many bad blocks”,

The comment notes to expect error on blank chip, though it doesn’t specify the error.

{

static const char *const messages[DHARA_E_MAX] = {

[DHARA_E_NONE] = "No error",

[DHARA_E_BAD_BLOCK] = "Bad page/eraseblock",

[DHARA_E_ECC] = "ECC failure",

[DHARA_E_TOO_BAD] = "Too many bad blocks",

[DHARA_E_RECOVER] = "Journal recovery is required",

[DHARA_E_JOURNAL_FULL] = "Journal is full",

[DHARA_E_NOT_FOUND] = "No such sector",

[DHARA_E_MAP_FULL] = "Sector map is full",

[DHARA_E_CORRUPT_MAP] = "Sector map is corrupted"

};

List of possible error codes doesn’t really solve that mystery.

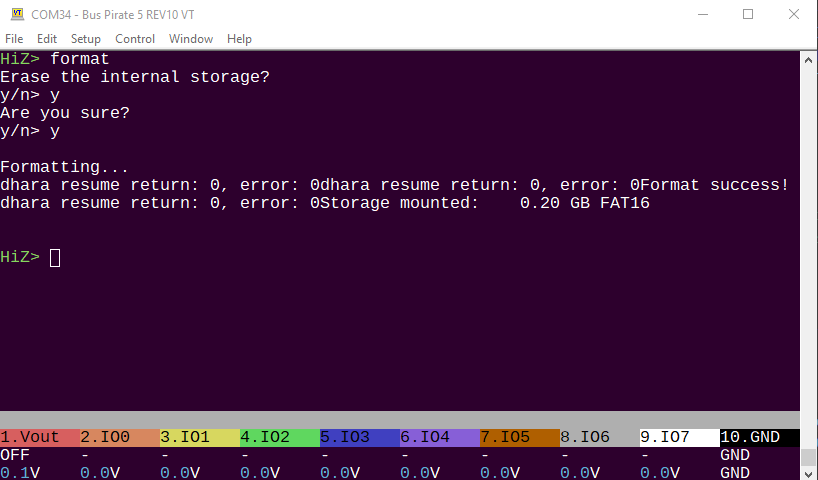

Formatting...

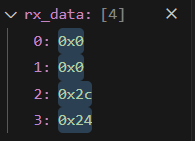

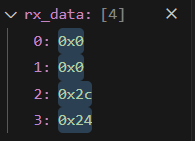

dhara resume return: -1, error: 3dhara resume return: -1, error: 3Error: filesystem not foundError: Format failed...

Error: filesystem not found

Enabled the printf error status in read and write disk, seems to give the same error.

bus_pirate5_rev10-2gbit-debug.zip (179.7 KB)

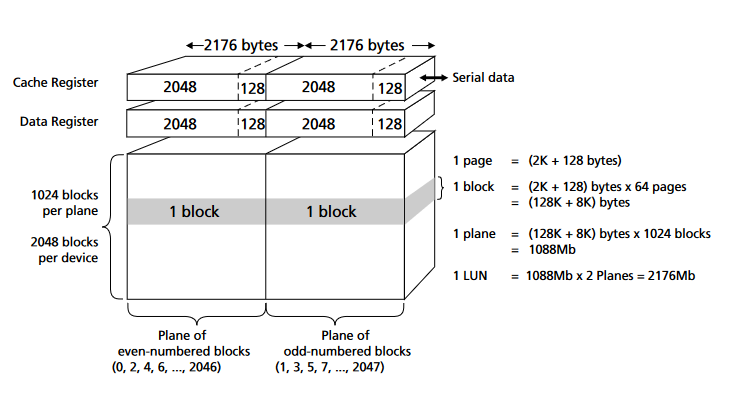

This firmware has the debug statements enabled. It is totally possible I have all bad block, I did a really nasty job with the hot air. Would be great to see if anyone with one of the professionally replaced 2Gbit chips has the same error/debug codes.