Starting a new ideas thread so we don’t get confused in the other two. In my mind these big changes would happen in an 8, rather than a 7. It feels like the SPI ADC will be a massive change, while the current 7REV1 stuff is manageable short-ish term.

Maybe this should be two threads?

1MHz SPI DAC

5volt SPI ADC

This is a really big one. The work involved in adjusting the firmware will be a big project.

I scanned back through various previous discussions and tried to piece together the chips we all looked at.

TPC5120 The 3Peak stuff is so promising, but we still have not managed to source anything from them and they won’t work directly with us. I did find a single supplier on taobao for 12kuai, but you never know if that is real, will inquire now. Digikey has it for 24RMB in 100s, szlcsc no longer lists it.

Update: 8.84 12 15kuai. After shuffling through two liar prices it seems we can get it for 15rmb in onesies.

TI ADS7952 (12 channels) and ADS7956 (16 channels) have spotty availability on szlcsc and cost 40-50kuai.

Assuming both chip are similar (previous discussion) here are some things I find interesting:

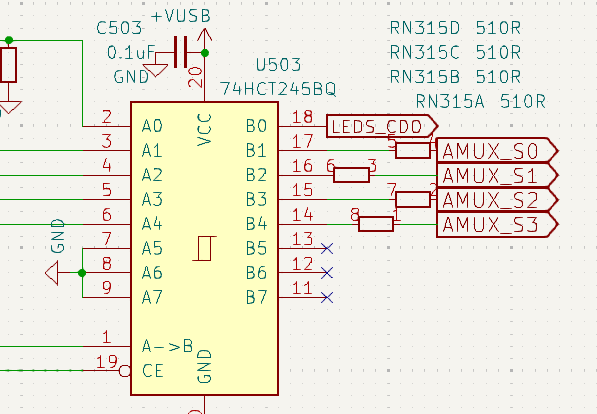

- IO pins can run at 3.3volts while the ADC and MUX run at VUSB

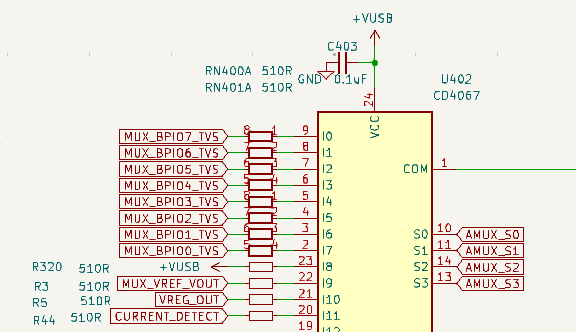

- It is a mux with and ADC, but the ADC and mux are connected externally. This is a great opportunity to buffer with an opamp and /2 so we can use a 3.3/3v reference.

- “There are two software selectable input ranges (0 V

to VREF and 0 V to 2 × VREF)” - not fully sure what this means, maybe it has an internal divider? In this case we don’t /2 externally, and then CURRENT_SENSE can also be moved to the external ADC (and be measured against the 3.3v reference) - Looking at the protocol, it can probably be managed completely with PIO and DMA, so I don’t need to worry about the shared SPI used with the display and NAND chip.

- It mentions adding a 150pf cap to each pin to help with settling between channels. Perhaps this is an opportunity to get rid of the opamp on each IO pin without reintroducting “the glitch”.

One reason I’m giving this a bit more thought at this juncture: this is what has to be added for the ruggedization or IO and VOUT.

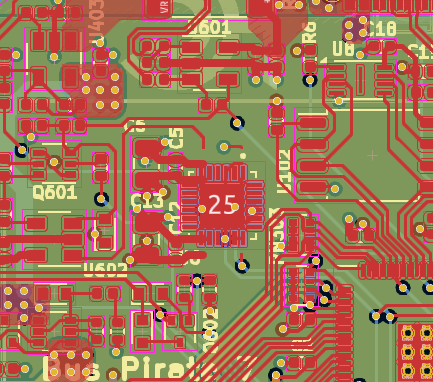

- The AUX voltage circuit will easily fit int he power supply area near the programming header.

- VOUT protection might fit in the VOUT area on the top left if the I2C dacs are removed

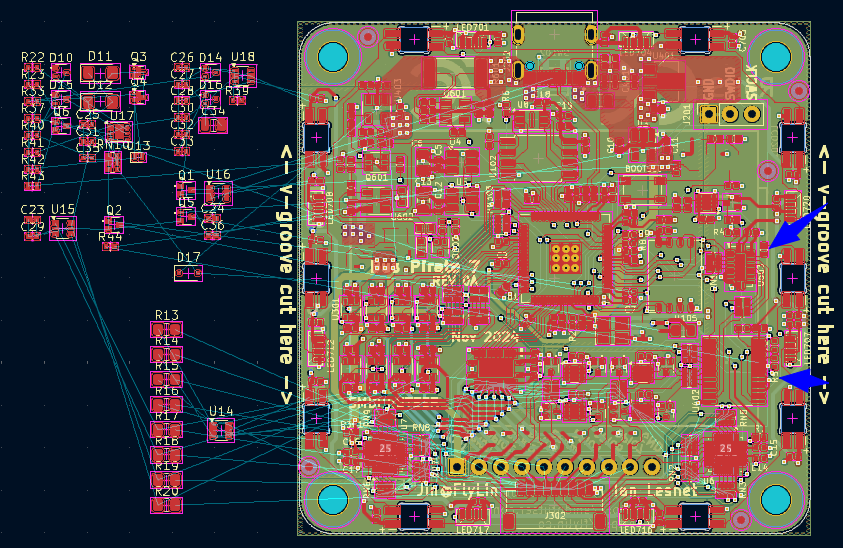

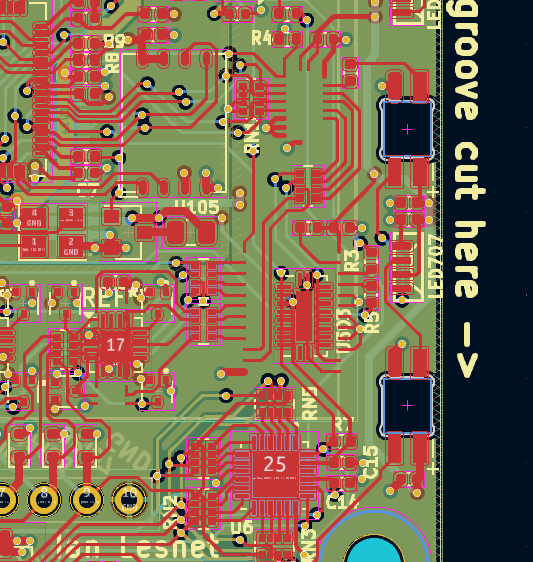

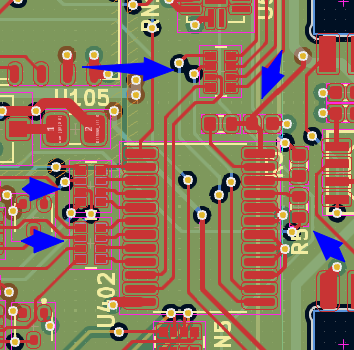

- In general it is a lot of components to add and we don’t have a ton of space. Removing the level shifter and MUX (blue arrows) and replacing them with a 5x5mm qfn could go a long way towards making everything fit.

Potentially removed pins:

- AMUX_OUT

- AMUX_S0-3

- Maybe CURRENT_SENSE

Potentially added pins:

- SPI bus

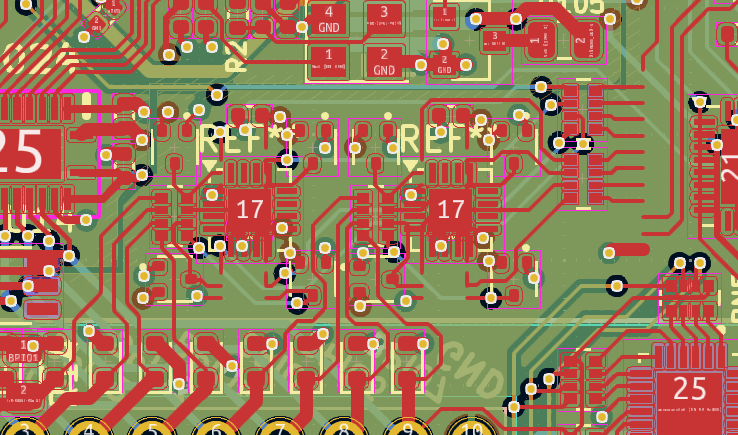

Move slow output signals to XL9555QF24 IO expander

The low hanging fruit (outputs only) looks to be 7 pins:

- Current_EN_OVERRIDE

- CURRENT_RESET

- CURRENT_EN

- ACTIVATE_VOUT

- DISPLAY_BACKLIGHT

- DISPLAY_RESET

- I2C_RESET (not sure this pin is strictly required, this is a REV0 test)

Kitchen sink

Some ideas I’ve had in the past that might make use of reclaimed pins:

- A 5-18volt SMPS. This would be super handy in a lot of situations. I discounted it in the past because “where would it output?”, but with the ruggedized VOUT and IO we could feed it to a pin (or pins, with a mux).

- Infrared emitter and receiver (with minor mods to case tooling using inserts).

- Your wishlist?

Epilogue

Thank you for following along as I collect my thoughts and make some notes.

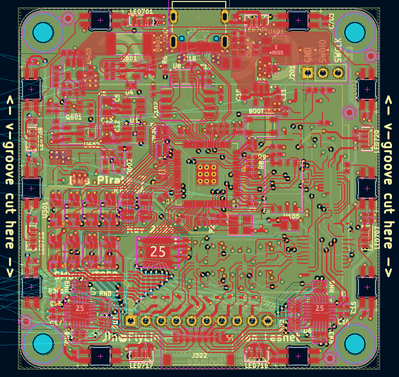

When the dust has settled on 7REV1 (shortly, I assume), I will ask our CAD guy if he can fit everything on the board. He usually can, even when I think it’s impossible ![]() I suspect this will be tough though.

I suspect this will be tough though.

If the board is unroutable, we could take a smaller step and then a bigger step:

- Test REV0 with the new optimized BOM changes and new hardware. If it works, clean off the crud (bad TVS diodes) and make a small batch. Call it BP7

- Speed along towards a BP8 with SPI ADC and make space for the ruggedizing components. Even without the IO expander, we can score 6 IO pins removing the AMUX. 4 recycled back into SPI, 2 for PWMs to control the voltage and current limit of VOUT.