Blinkinlabs (one of our distributors) pointed me to a Arduino project for reading and writing SDRAMM/DDR2/DDR3/DDR4/DDR5 PC RAM parameter tables. The excerpts here are GPL 3.0 licensed.

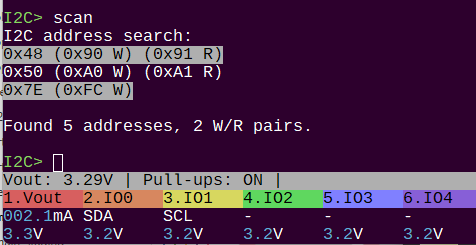

All kinds of PC RAM since SDRAM have an I2C EEPROM that stores various info about the RAM stick and control version factors.

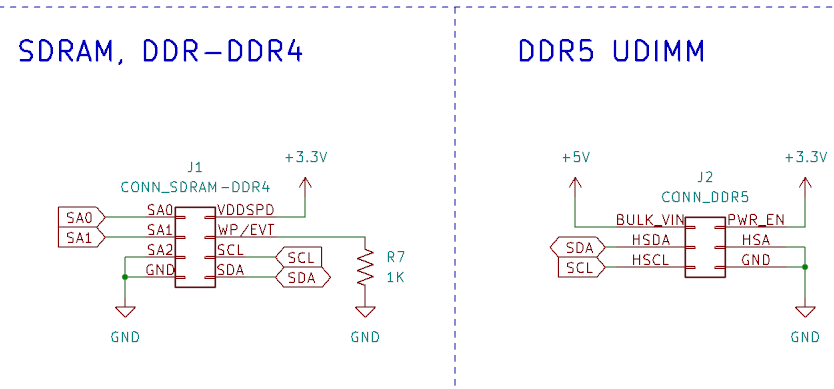

SDRAMM/DDR2/DDR3/DDR4 require a 9 volt programming voltage to make changes (SA0). SA1 is another 3.3volt control signal (WP?). SCL and SDA are the standard 3.3volt I2C clock and data pins.

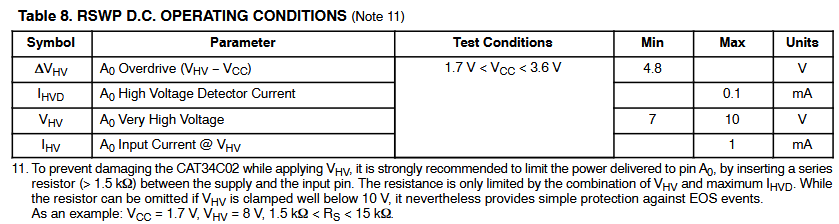

Onsemi CAT34C02 is an example of a DDR2 EEPROM chip. We can see here in the datasheet the Vhv is 7 to 10 volts to do certain stuff (write protect, unlock, stuff like that, let’s not get into details).

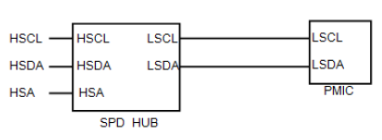

DDR5 is different in an interesting way. The EEPROM is now part of the “Serial Presence Detect hub” or SPD hub.

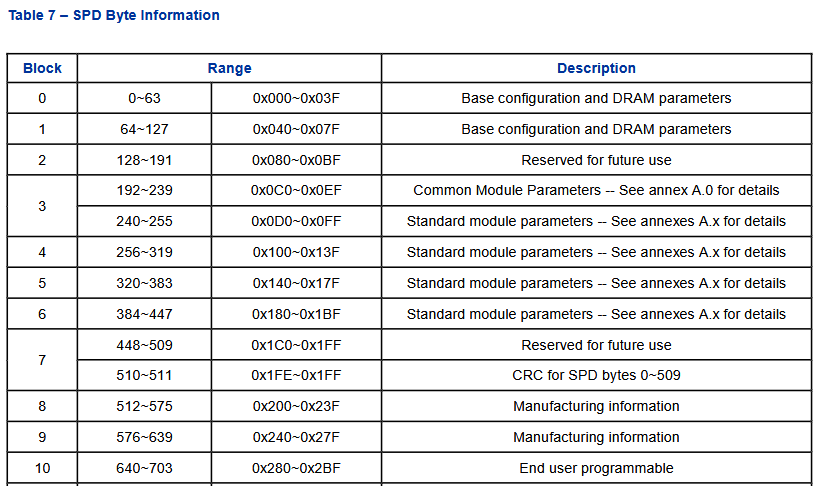

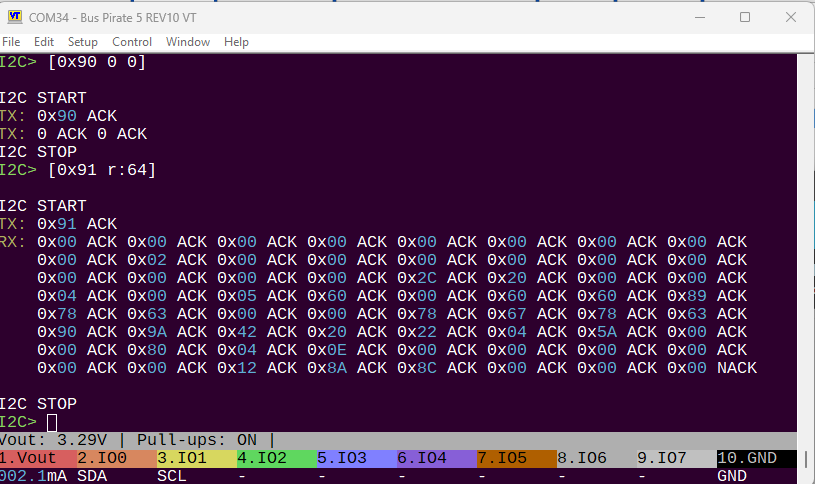

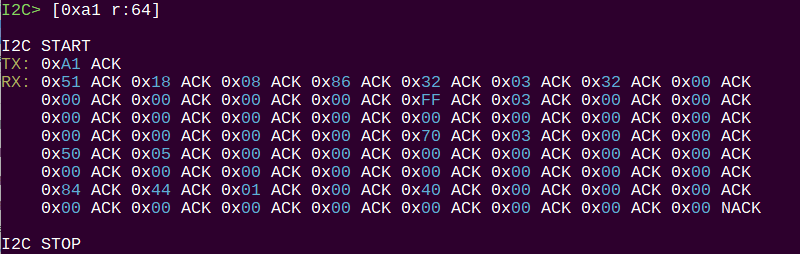

Here is the EEPROM memory map for an off brand DDR5 RAM.

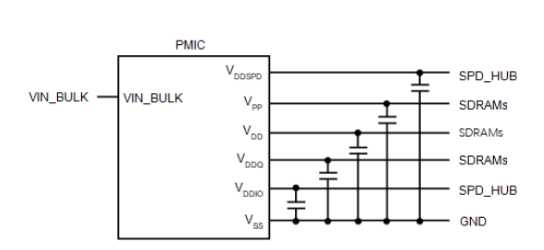

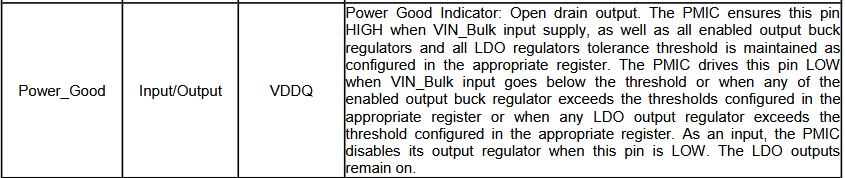

The SPD hub in turn controls a Power Management IC (PMIC). This chip takes a single 5volt supply from a single pin on the RAM module and outputs all the voltages needed by the RAM chips. This eliminates the need for an ever increasing number of voltage pins on the module, and frees pins for new features. Smart!

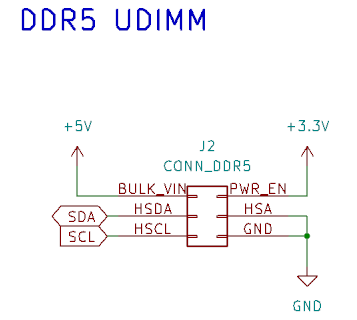

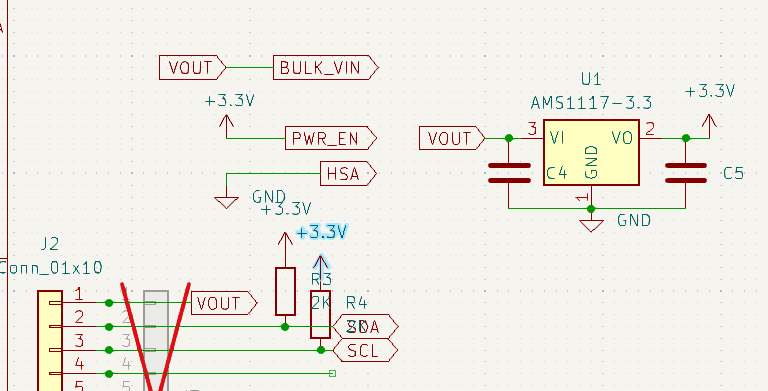

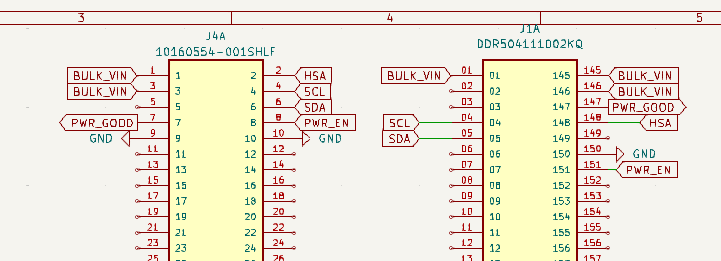

Looking at that DDR5 example from the Arduino project again, and we see the BLUK_IN pin. This is not a programming voltage like previous generations used 9V, instead it is a single supply that is regulated by the PMIC to power the module.

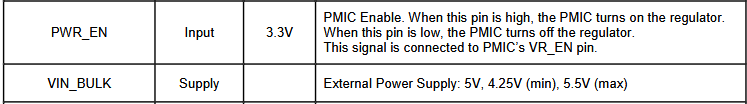

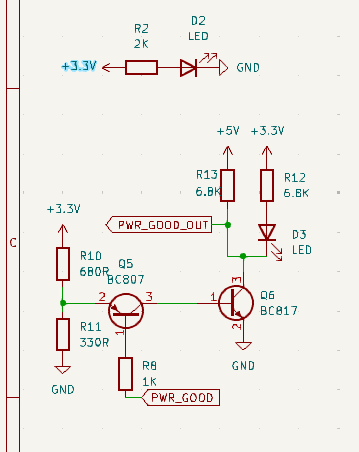

PWR_EN controls the PMIC, high/3.3volts to enable.

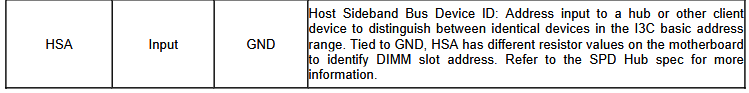

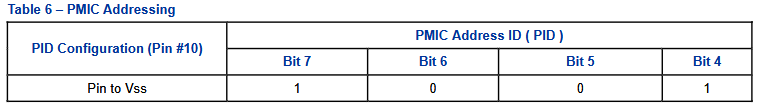

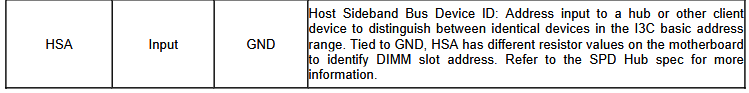

HSA sets the module I2C address, so a computer motherboard can tell the modules apart.

Each DIMM slot on a motherboard has a different resistor value attached between this pin and ground. It sets the I2C address according to some spec we don’t need to get into. In the Arduino project it is just tied to ground.

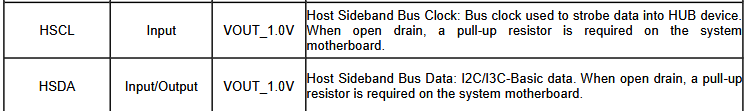

SDA and SCL are still there, though the chip can be elevated from I2C to an I3C mode. I’m not sure about the 1.0 volt note there.

Taking it further

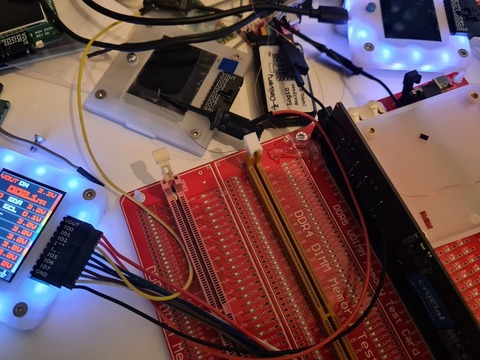

Starting with DDR5 because it is current and it might actually be useful for overclocking modern rigs. Also because we don’t need to deal with the 9 volt programming voltage. An ewaste stick of DDR5 RAM should arrive shortly. I bought a DDR3-5 tester board with nice sockets, but GRRRRR it doesn’t break out any of the needed IO pins.

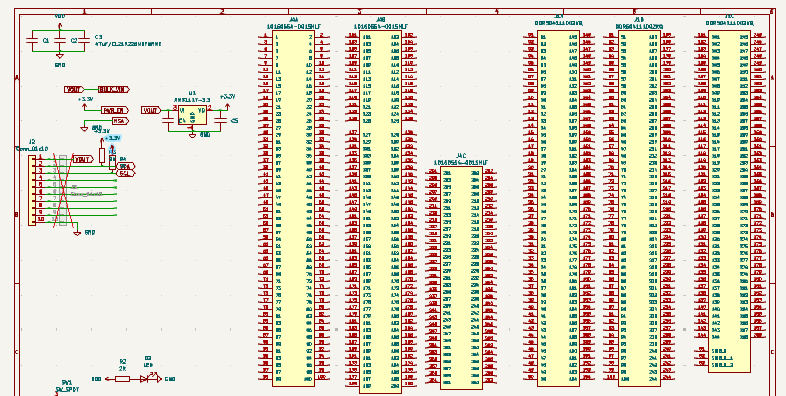

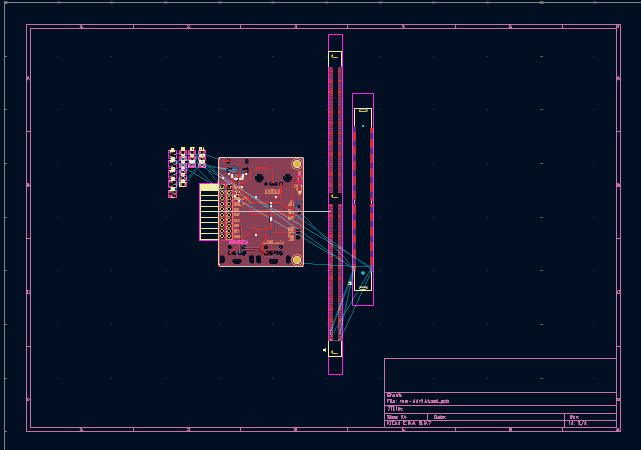

Quick mock up of a DDR5 UDIMM and SODIMM plank. Those sockets are huge and $$$.

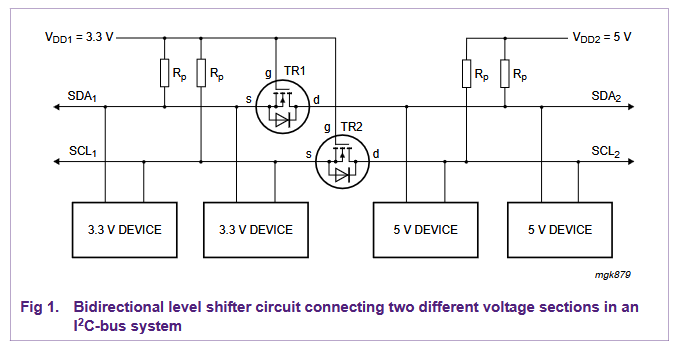

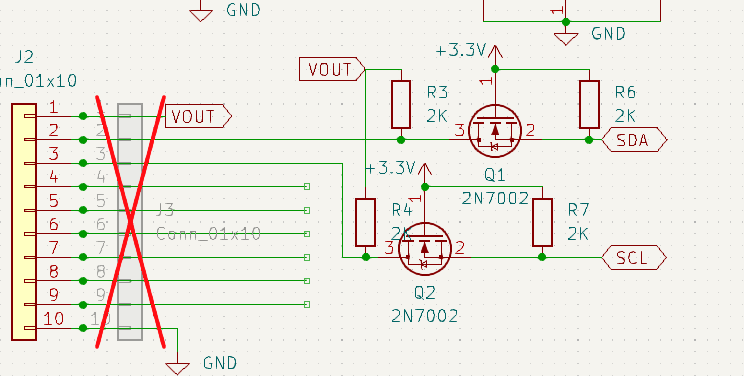

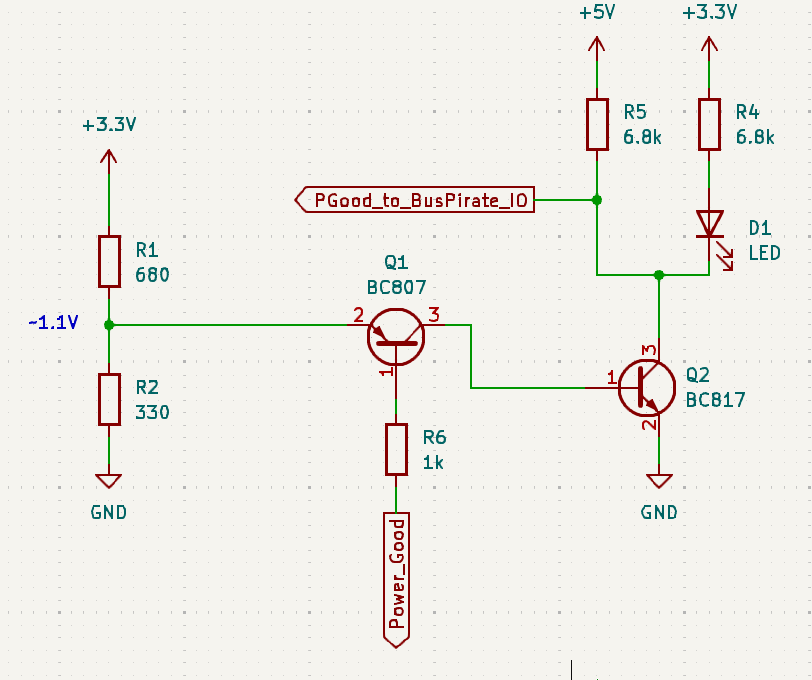

The IO needs a 3.3volt supply, but the bulk_vin needs 5 volts. My initial thought is to use the Bus Pirate VOUT at 5 volts. A regulator on the board provides 3.3volt for the control signals and I2C pull-up resistors. This isn’t ideal, as a wrong voltage on the I2C pin could break a module, so maybe some kind of simple bidirectional level shifter or a protection zener (yucky, probably). On the other hand the Arduino project above is running at 5volts and relies on the pins to stay open drain

Resources